Home Search Collections Journals About Contact us My IOPscience

Low-Loss Amorphous Silicon Multilayer Waveguides Vertically Stacked on Silicon-on-Insulator Substrate

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2011 Jpn. J. Appl. Phys. 50 120208

(http://iopscience.iop.org/1347-4065/50/12R/120208)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 131.112.10.178

This content was downloaded on 19/07/2017 at 16:47

Please note that terms and conditions apply.

You may also be interested in:

<u>Hydrogenated Amorphous Silicon Carbide Optical Waveguide for Telecommunication Wavelength</u>

Applications

Yuya Shoji, Koichi Nakanishi, Youichi Sakakibara et al.

Layer-to-Layer Grating Coupler Based on Hydrogenated Amorphous Silicon for Three-Dimensional Optical Circuits

Joonhyun Kang, Yuki Atsumi, Manabu Oda et al.

Low-Loss GalnAsP Wire Waveguide on Si Substrate with Benzocyclobutene Adhesive Wafer Bonding for Membrane Photonic Circuits

Jieun Lee, Yasuna Maeda, Yuki Atsumi et al.

<u>Transmission Characteristics of Hydrogenated Microcrystalline Silicon Wire Waveguide at a</u> Wavelength of 1.55 µm

Ryohei Takei, Shoko Manako, Emiko Omoda et al.

ZnO Channel Waveguides for Nonlinear Optical Applications

Edgar Yoshio Morales Teraoka, Tomohiro Kita, Atsushi Tsukazaki et al.

Silicon Ring Optical Modulator with p/n Junctions Arranged along Waveguide for Low-Voltage Operation

Yoshiteru Amemiya, Ryuichi Furutani, Masataka Fukuyama et al.

Compact and Polarization-Independent Variable Optical Attenuator Based on a Silicon Wire Waveguide with a Carrier Injection Structure

Hidetaka Nishi, Tai Tsuchizawa, Toshifumi Watanabe et al.

DOI: 10.1143/JJAP.50.120208

## Low-Loss Amorphous Silicon Multilayer Waveguides Vertically Stacked on Silicon-on-Insulator Substrate

JoonHyun Kang<sup>1</sup>, Yuki Atsumi<sup>1</sup>, Manabu Oda<sup>1</sup>, Tomohiro Amemiya<sup>1,2</sup>, Nobuhiko Nishiyama<sup>1\*</sup>, and Shigehisa Arai<sup>1,2</sup>

Received September 27, 2011; accepted October 20, 2011; published online November 28, 2011

Low-loss amorphous-silicon (a-Si) waveguides comprising three vertically stacked layers prepared on silicon-on-insulator substrates are demonstrated. We have fabricated multilayer a-Si waveguides and investigated their loss characteristics; this is the first such investigation to our knowledge. All the process temperatures were regulated below 400 °C for the complementary metal oxide semiconductor (CMOS) backend process compatibility. When the surface roughness and sidewall roughness were decreased, the propagation loss decreased to 3.7 dB/cm even in the case of the third layer a-Si waveguide. Such low-loss waveguides can be effectively applied to realize multilayer stacked optical devices. © 2011 The Japan Society of Applied Physics

ptical interconnections on silicon (Si) large-scale integrated circuits (LSIs) are attracting attention as a breakthrough technology for overcoming the performance limitations of electrical interconnections as well as for realizing high-density systems-on-chip (SoCs).<sup>1,2)</sup> Further, it is expected that the basic material for these optical interconnections will be Si-based materials since they can be integrated with Si-LSI, thereby ensuring sufficient process compatibility. In addition, Si has a large refractive index difference when paired with SiO<sub>2</sub> and enables the fabrication of sub-micron optical waveguides, thereby leading to high-density optical circuits. Several parts of optical components having silicon-on-insulator (SOI) substrates have already been demonstrated.<sup>3–5)</sup>

However, in order to integrate the optical components on an LSI through backend processes, all the fabrication processes for the optical components should be regulated to below 400 °C in order to avoid damages to the complementary metal-oxide-semiconductor (CMOS) layer. Amorphous silicon (a-Si) is the most promising material for optical circuits since it can be deposited under low-temperature conditions by plasma-enhanced chemical-vapor-deposition (PECVD).<sup>6)</sup> In addition, multilayer stacking can be realized by depositing a-Si and SiO<sub>2</sub> alternately, and high-density three-dimensional optical circuits can thereby be realized on the LSI. Recently, the ultrafast nonlinear characteristics of a-Si waveguides have attracted additional attention.<sup>7)</sup> Many researchers have demonstrated low-loss a-Si waveguides, while a few researches have been conducted on light transmissions between a-Si waveguides placed on top and crystalline Si (c-Si) waveguides placed at the bottom.<sup>8–11)</sup> However, to our knowledge, there have been no reports on the characteristics when more than three stacked layers of Si waveguides are placed. In this paper, we have investigated, for the first time to our knowledge, the loss characteristics of a-Si waveguides prepared through multilayer stacking processes and the dependence of the performance on the fabrication processes.

Multilayer a-Si waveguides were fabricated on a SOI wafer consisting of a 3- $\mu$ m buried oxide (BOX) layer and a 220-nm c-Si layer. The core width and height of the a-Si waveguides were 450 and 220 nm, respectively, for all the layers. The schematic images of each layer are illustrated

**Fig. 1.** (Color online) (a) Schematic diagrams of c-Si (first layer) and a-Si waveguides (second and third layers) and (b) cross-sectional and (c) top SEM images of the third layer of the a-Si waveguide formed by PP-RIE.

in Fig. 1(a), and the cross-sectional scanning electron microscope (SEM) image of the third layer waveguide is shown in Fig. 1(b). The fabrication process is described below.

The waveguides were patterned by electron beam lithography (EBL) with a double-layered positive resist Zeon ZEP520A and with a C<sub>60</sub>-containing microcomposite in order to enhance the etching selectivity between the resist and Si-films. 12) The waveguide pattern was formed by dry etching wherein two types of dry etching systems parallel-plate reactive-ion-etching (PP-RIE) and inductively-coupled-plasma (ICP) RIE — were used. For the second layer fabrication, c-Si layer was removed and 1- $\mu m$ -thick  $SiO_2$  was deposited by PECVD from tetraethyl orthosilicate (TEOS) [TEOS flow rate: 14 sccm, O<sub>2</sub> flow rate: 300 sccm, gas pressure: 120 Pa, power: 250 W, deposition temperature: 300 °C]. Subsequently, a-Si was deposited by PECVD on the SiO<sub>2</sub> layer as the second layer. The third layer was also fabricated by repeating the previous processes. The SEM image from the top of the third layer waveguide is shown in Fig. 1(c). The sidewall roughness values ( $3\sigma'$  values;  $\sigma'$  is the standard deviation) of the waveguides after PP-RIE and ICP-RIE were measured by

<sup>&</sup>lt;sup>1</sup>Department of Electrical and Electronic Engineering, Tokyo Institute of Technology, Meguro, Tokyo 152-8552, Japan

<sup>&</sup>lt;sup>2</sup> Quantum Nanoelectronics Research Center, Tokyo Institute of Technology, Meguro, Tokyo 152-8552, Japan

a-Si (220 nm) a-Si (220 nm) SiO<sub>2</sub> film (1.0 μm) c-Si (220 nm) SiO<sub>2</sub> film (1.0 µm) SiO<sub>2</sub> film (1.0 µm) SiO<sub>2</sub> film (3.0 μm) SiO<sub>2</sub> film (3.0 μm) SiO<sub>2</sub> film (3.0 µm) Si substrate Si substrate Si substrate (a) 300 nm 300 nm 3σ' : 3.3 nm a-Si SiO2 a-Si SiO2 SiO (c)

<sup>\*</sup>E-mail address: n-nishi@pe.titech.ac.jp

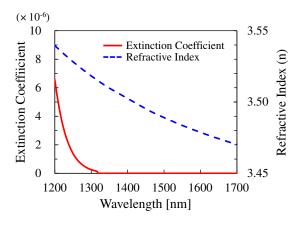

Fig. 2. (Color online) Wavelength dependence of the refractive index and extinction coefficient for a-Si film.

Table I. Surface roughness of each layer (RMS).

| Measured               | First  | Second |       | Third  |       |

|------------------------|--------|--------|-------|--------|-------|

| point                  | (c-Si) | 130 Pa | 30 Pa | 130 Pa | 30 Pa |

| σ <sub>Top</sub> (nm)  | 0.17   | 1.06   | 0.30  | 1.03   | 0.52  |

| $\sigma_{Bottom}$ (nm) | 0.18   | 0.24   | 0.24  | 0.37   | 0.36  |

the function of the SEM (Hitachi S-5000) to be 3.3 and  $2.4 \,\mathrm{nm}$ , respectively; further, the sidewall angles of each waveguide were 81 and  $85^{\circ}$ , respectively.

It is well known that a-Si tends to have high optical absorptions under certain conditions. We measured the extinction coefficient and refractive index of the deposited a-Si by using the ordinary ellipsometry method. The deposition conditions were as follows. SiH<sub>4</sub> flow rate: 100 sccm, Ar flow rate: 100 sccm, power: 100 W, and deposition temperature: 300 °C. Figure 2 shows the wavelength dependence of the refractive index and extinction coefficient for the a-Si film. From the results, the real part of the refractive index was 3.48, and the material absorption in our deposition film at 1.55-µm wavelength can be expected to be negligible.

The surface roughness of each layer before and after the deposition of the a-Si layer was measured by using an atomic force microscope (AFM); these roughness values are listed in Table I as root-mean-square (RMS) values.  $\sigma_{\rm bottom}$  refers to the surface roughness before a-Si deposition for each layer (in other words, the roughness of the top of the SiO<sub>2</sub> film). For the first layer (c-Si), the value was measured after etching the c-Si film.  $\sigma_{\rm top}$  refers to the roughness values after the a-Si deposition. The table lists the RMS roughness for the a-Si films under the deposition pressures of 30 and 130 Pa during PECVD. The top surface roughness of a-Si film is inferior to that of c-Si film when the deposition pressure was 130 Pa.

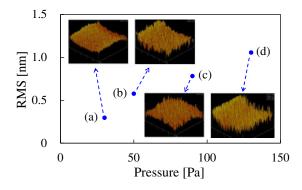

The top surface roughness as well as the corresponding AFM image as a function of the deposition pressure is shown in Fig. 3. As the deposition pressure decreased, the surface roughness reduced from 1.06 nm (130 Pa) to 0.30 nm (30 Pa), and this can be attributed to increases in the migration length at lower deposition pressures. When the deposition pressure was 30 Pa, the surface roughness was 40–50% higher after the deposition of the a-Si layer and approximately twice

**Fig. 3.** (Color online) Surface roughness of a-Si film as a function of deposition pressure in the form of AFM images, (a) 30, (b) 50, (c) 90, and (d) 130 Pa.

and thrice that of the c-Si layer after the depositions of the second and third a-Si layers, respectively.

The propagation losses of a-Si waveguides fabricated by PP-RIE [CF<sub>4</sub> gas flow: 10 sccm, pressure: 0.3 Pa, bias power: 20 W, waveguide width: 450 nm, sidewall roughness: 3.3 nm (3σ' value), sidewall angle: 81°] were measured by coupling transverse-electric (TE) polarized light from a tunable laser emitting at around 1.55-μm wavelength. The light was coupled to the waveguides through tip lensed single-mode fibers, and the propagation losses were calculated by using the cutback method. For the deposition pressure of 130 Pa, the propagation losses of the first c-Si layer, the second, and the third a-Si layers were 6.0, 10.2, and 12.0 dB/cm, respectively. The propagation loss of the second layer a-Si waveguide with the deposition pressure of 30 Pa was 7.0 dB/cm, i.e., only 1 dB/cm higher than that of the first layer c-Si waveguide.

Previous experiments had focused on the surface roughness of multilayer waveguides. In our study, we changed the etching machine from PP-RIE to ICP-RIE in order to cut down the sidewall roughness. Low process pressures can be applied by using ICP-RIE that assists the directionality of the ion flux in the chamber, and moreover, these characteristics lead to better vertical shapes during etching process.<sup>13)</sup> We fabricated multilayer a-Si waveguides up to the third layer with ICP-RIE [CF<sub>4</sub> gas flow: 10 sccm, pressure: 0.03 Pa, ICP power: 5 W, bias power: 150 W]. The deposition pressure of 30 Pa was used for a-Si; here were no noticeable changes in the surface roughness between PP-RIE and ICP-RIE. Further, the waveguide width was changed to 500 nm. We assumed that the propagation loss reduces with wider widths even though the effect is negligible. The sidewall angle improved from 81 to 85° when the ICP-RIE etching process was used, and the sidewall roughness  $(3\sigma')$  value was estimated to be 2.4 nm. The propagation losses of the first layer c-Si waveguide and the second and third layer a-Si waveguides were measured to be 1.6, 3.8, and 3.7 dB/cm, respectively.

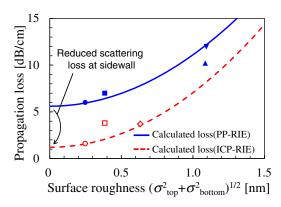

To determine the reasons for the propagation loss degradation with multilayer waveguides, we plotted the measured propagation losses against the sum of the RMS values of the top and bottom surface roughness values  $(\sigma_{\text{top}}^2 + \sigma_{\text{bottom}}^2)^{1/2}$  (Fig. 4). The solid line in the figure shows the calculated results of the scattering loss after considering

**Fig. 4.** (Color online) Measured losses (diamonds) and calculated losses due to the surface roughness of the Si waveguides. (Further information about plotted data is listed in Table II.)

the surface roughness and sidewall roughness for the PP-RIE-etched waveguides. <sup>14–16)</sup> The scattering loss at the sidewall was assumed to be 5.6 dB/cm. The measured propagation losses agreed well with the calculated ones, and this indicates that the primary cause of the propagation loss difference between the c-Si and a-Si waveguides is the scattering loss from the surface and not the material absorption of a-Si. Therefore, reducing the surface roughness as well as side wall roughness is very important for fabricating low-loss a-Si waveguides.

The relationship between the scattering loss and surface roughness is also calculated as a dashed line in Fig. 4 for the ICP-RIE etched waveguides; the scattering loss at the sidewall was estimated to be 1.2 dB/cm. The propagation loss drastically reduced in these samples as a result of the improvements in the sidewall roughness. All the propagation losses of each waveguide are summarized in Table II.

In summary, we have fabricated multilayer a-Si waveguides and investigated their loss characteristics for the first time to our knowledge. Further, we have confirmed the deterioration of the surface roughness for multilayer waveguides. The surface roughness and sidewall roughness dependence of the propagation loss have been described and the effects of the roughness values have been estimated separately. When the deposition pressure of a-Si was decreased from 130 to 30 Pa, the scattering from the surface roughness decreased, leading to improvements in the propagation loss. The scattering loss from the sidewall roughness also decreased when the etching method was changed from PP-RIE to ICP-RIE. The propagation losses

**Table II.** The propagation loss of each layer waveguide.

| Etablica mathad | First      | Second |              | Third  |       |

|-----------------|------------|--------|--------------|--------|-------|

| Etching method  | (c-Si)     | 130 Pa | 30 Pa        | 130 Pa | 30 Pa |

| PP-RIE (dB/cm)  | <b>6.0</b> | ▲ 10.2 | <b>1</b> 7.0 | ▼ 12.0 |       |

| ICP-RIE (dB/cm) | ○ 1.6      | _      | □ 3.8        | _      | ♦3.7  |

of the first layer c-Si waveguide and second and third layer a-Si waveguides were obtained as 1.6, 3.8, and 3.7 dB/cm, respectively.

Acknowledgments The authors would like to thank professor M. Asada, professor T. Mizumoto, professor Y. Miyamoto, and professor M. Watanabe for their help. The authors also thank Mr. S. Tamura for the assistance while conducting all the experiments and Minebea for the ellipsometry measurements. This research was supported by the Ministry of Education, Culture, Sports, Science and Technology (MEXT) and the Japan Society for the Promotion of Science (JSPS) under Grants-in-Aid for Scientific Research (19002009, 22360138, 21226010), and also by JSPS and the Council for Science and Technology Policy (CSTP) under the Funding program for World-Leading Innovative R&D on Science and Technology (FIRST) program, and by the Ministry of Internal Affairs and Communications under the Strategic Information and Communications R&D Promotion Programme (SCOPE).

- 1) F. Xia, L. Sekaric, and Y. Vlasov: Nat. Photonics 1 (2007) 65.

- 2) Y. Vlasov, W. M. J. Green, and F. Xia: Nat. Photonics 2 (2008) 242.

- T. Tsuchizawa, K. Yamada, H. Fukuda, T. Watanabe, J. Takahashi, M. Takahashi, T. Shoji, E. Tamechika, S. Itabashi, and H. Morita: IEEE J. Sel. Top. Quantum Electron. 11 (2005) 232.

- P. Dumon, G. Priem, L. R. Nunes, W. Bogaerts, D. V. Thourhout, P. Bienstman, T. K. Liang, M. Tsuchiya, P. Jaenen, S. Beckx, J. Wouters, and R. Baets; Jpn. J. Appl. Phys. 45 (2006) 6589.

- Y. Atsumi, K. Inoue, N. Nishiyama, and S. Arai: Jpn. J. Appl. Phys. 49 (2010) 050206.

- 6) J. V. Campenhout, W. M. J. Green, S. Assefa, and Y. Vlasov: Opt. Express 17 (2009) 24020.

- Y. Shoji, T. Ogasawara, T. Kamei, Y. Sakakibara, S. Suda, K. Kintaka, H. Kawashima, M. Okano, T. Hasama, H. Ishikawa, and M. Mori: Opt. Express 18 (2010) 5668.

- B. Han, R. Orobtchouk, T. Benyattou, P. R. A. Binetti, S. Jeannot, J. M. Fedeli, and X. J. M. Leijtens: Proc. 13th European Conf. Integrated Optics, 2007, ThF3.

- R. Sun, M. Beals, A. Pomerene, J. Cheng, C. Hong, L. Kimerling, and J. Michel: Opt. Express 16 (2008) 11682.

- S. K. Selvaraja, E. Sleeckx, M. Schaekers, W. Bogaerts, D. V. Thourhout, P. Dumon, and R. Baets: Opt. Commun. 282 (2009) 1767.

- R. Sun, K. McComber, J. Cheng, D. K. Sparacin, M. Beals, J. Michel, and L. C. Kimerling: Appl. Phys. Lett. 94 (2009) 141108.

- K. Inoue, D. Plumwongrot, N. Nishiyama, S. Sakamoto, H. Enomoto, S. Tamura, T. Maruyama, and S. Arai: Jpn. J. Appl. Phys. 48 (2009) 030208.

- I. Adesida, C. Youtsey, A. T. Ping, F. Khan, L. T. Romano, and G. Bulman: MRS Internet J. Nitride Semicond. Res. 4S1 (1999) G1.4.

- 14) P. K. Tien: Appl. Opt. 10 (1971) 2395.

- 15) F. P. Pyne and J. P. R. Lancey: Opt. Quantum Electron. **26** (1994) 977.

- 16) Y. A. Vlasov and S. J. McNab: Opt. Express 12 (2004) 1622.