# Performance Improvement of HfS<sub>2</sub> Transistors by Atomic Layer Deposition of HfO<sub>2</sub>

Toru Kanazawa, Tomohiro Amemiya, *Member, IEEE*, Vikrant Upadhyaya, Atsushi Ishikawa, Kenji Tsuruta, Takuo Tanaka, and Yasuyuki Miyamoto, *Senior Member, IEEE*

Abstract—Hafnium disulfide (HfS $_2$ ) is one of the transition metal dichalcogenides which is expected to have the high electron mobility and the finite bandgap. However, the fabrication process for HfS $_2$ -based electron devices is not established, and it is required to bring out the superior transport properties of HfS $_2$ . In this report, we have investigated the effects of the atomic layer deposited HfO $_2$  passivation on the current properties of HfS $_2$  transistors. HfO $_2$  passivation of the HfS $_2$  surface enhanced the drain current and significantly reduced the hysteresis. Moreover, HfO $_2$  passivation allows the use of a higher annealing temperature and further improvement of the drain current.

Index Terms—MOSFETs, transition metal dichalcogenides, hafnium disulfide, atomic layer deposition.

## I. INTRODUCTION

**¬** HE discovery of the graphene [1], [2] resulted in an enormous interest in the field of two-dimensional (2D) materials with atomic layer thickness. Graphene exhibits ultra-high mobility [3] with many other attractive properties and its device applications, such as transistors, photodetectors, and gas sensors have been widely studied. However, the zero bandgap in graphene makes it difficult to suppress the off leakage current of metal-oxide-semiconductor field-effect transistors (MOSFETs) [4], which is one of the most important performance parameters for low-power logic applications. Therefore, in recent years, various types of transition metal dichalcogenides (TMDs), such as MoS<sub>2</sub> [5], [6], WS<sub>2</sub> [7], and WSe<sub>2</sub> [8], have been investigated as post-graphene 2D materials for extremely scaled low power and high-speed logic applications. These TMDs have both the finite bandgap and extremely thin layer structure (<1 nm), which is attractive for MOSFETs with a channel length less than 10 nm.

Manuscript received September 30, 2016; accepted January 21, 2017. Date of publication January 31, 2017; date of current version July 7, 2017. This work was supported by the Japan Society for the Promotion of Science KAKENHI under Grant JP16H00905. The review of this paper was arranged by Associate Editor NANO2016 Guest Editors.

- T. Kanazawa, T. Amemiya, V. Upadhyaya, and Y. Miyamoto are with the Tokyo Institute of Technology, Meguro 152-8552, Japan (e-mail: kanazawa. t.aa@m.titech.ac.jp; amemiya.t.ab@m.titech.ac.jp; upadhyaya.v.aa@m.titech.ac.jp; miya@pe.titech.ac.jp).

- A. Ishikawa and K. Tsuruta are with the Okayama University, Okayama 700-8530, Japan (e-mail: a-ishikawa@okayama-u.ac.jp; tsuruta@okayama-u.ac.jp).

- T. Tanaka is with the RIKEN, Wako 351-0918, Japan (e-mail: t-tanaka@riken.jp).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TNANO.2017.2661403

| Parameter                                    | Ref. | HfS <sub>2</sub> | MoS <sub>2</sub> | WSe <sub>2</sub> |

|----------------------------------------------|------|------------------|------------------|------------------|

| $\mu_{n,AP}^{\dagger}$ [cm <sup>2</sup> /Vs] | [10] | 1,833            | 340              | 703              |

| m* [m <sub>0</sub> ]                         | [10] | 0.24/3.3         | 0.45             | 0.33             |

| E <sub>g</sub> [eV]                          | [11] | 1.23             | 1.59             | 1.32             |

| †acoustic phonon limited electron mobility   |      |                  |                  |                  |

| (b)                                          |      |                  |                  |                  |

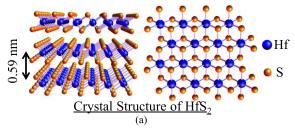

Fig. 1. (a) Crystal structure and (b) fundamental electrical properties of HfS<sub>2</sub>.

Hafnium disulfide (HfS<sub>2</sub>) is a semiconducting TMD, which has a 2D crystal structure with octahedral coordination and the single layer thickness of 0.59 nm [9]. HfS<sub>2</sub> is expected to exhibit high acoustic phonon limited electron mobility ( $\sim$ 1,800 cm<sup>2</sup>/Vs) [10] and adequate bandgap ( $\sim$ 1.2 eV) [11] as shown in Fig. 1.

In our previous studies, we demonstrated the device operation of few-layer HfS2 MOSFETs with robust current saturation and good on/off ratio [12], [13]. Some other groups also reported on HfS<sub>2</sub> applications based on theoretical calculations [14], device fabrication [15]-[17], and crystal growth [18]. However, the maximum drain current of the reported HfS2 FETs is only several hundreds of nA/ $\mu$ m or less because the fabrication process for HfS2 MOSFETs remains to be established. In addition, in several cases, large hysteresis and severe instability of drain current against measurement sequences were observed in the atmosphere owing to charge traps. Moreover, time-dependent degradation of FET current in air with high humidity simultaneously appeared. Atmospheric degradation is one of the critical issues in the realization of high performance HfS<sub>2</sub> FETs and the evaluation of material properties. The degradation seems to be caused by the reaction between the HfS<sub>2</sub> surface and moisture, oxygen and other contaminants in air. To prevent this degradation and instability, the surface of the 2D material should be passivated and isolated from the atmosphere [16] to reduce the

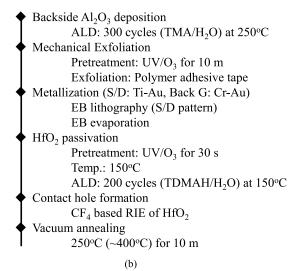

Fig. 2. (a) Schematic image of the device structure of  $HfS_2$  back-gate FET with  $HfO_2$  passivation and optical images of after exfoliation and after  $HfO_2$  passivation. (b) Fabrication process flow. (a) Device structure (b) Fabrication process.

trap states and absorption of gas atoms, respectively. Previously, we attempted to protect the surface by PMMA spin-coated on HfS<sub>2</sub> FET [19]. Although it indicated some improvement in current performance, the protection using PMMA was not robust enough to protect the surface from atmospheric degradation for longer duration.

In this report, we investigate the effects of surface passivation by atomic layer deposition (ALD) of the HfO $_2$  dielectric, which is commonly used as a high-k gate insulator in MOSFETs. A significant reduction of hysteresis was obtained compared to bare devices measured in the atmosphere. Additional annealing after HfO $_2$  passivation enhances the device performance of HfS $_2$  FETs and a maximum drain current of 4  $\mu$ A/ $\mu$ m was observed, which is higher than all reported values for the HfS $_2$  channel with solid gate dielectrics.

## II. DEVICE STRUCTURE AND FABRICATION

Fig. 2 shows the schematic of the fabricated device structure along with the optical microscope images of the HfS<sub>2</sub> flake after exfoliation and the completed device structure, which is covered by HfO<sub>2</sub>. The HfO<sub>2</sub> cap layer resulted in a change in the color of flakes and back-gate insulator. Multilayer HfS<sub>2</sub> is used as the channel of the MOSFETs. Although the number of layers was not directly measured in this study, the thickness may be

approximately 4-6 layers (2.4-3.6 nm); this was estimated based on the color, brightness, and contrast compared with those from previous studies. An  $HfO_2$  passivation layer was deposited to encapsulate the channel and contacts. Gate bias was applied from the degenerately n-doped Si substrate as the back gate through the  $Al_2O_3$ .

The fabrication process of MOSFETs based on mechanical exfoliation is as follows. First, the back-gate Al<sub>2</sub>O<sub>3</sub> insulator is fabricated by performing 300 cycles of ALD (around 30 nm thick) on the n<sup>+</sup>-Si substrate at 300 °C with trimethylaluminum (TMA) and water as precursors. Second, HfS<sub>2</sub> flakes were transferred to the substrate by micromechanical exfoliation using polymer adhesive tape; this was accomplished by the pre-treatment of the oxide surface by UV/ozone cleaner for 10 m to remove the hydrocarbon-based contamination and facilitate the contact between HfS<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>. Source/drain (S/D) electrodes and back gate contact were fabricated by electron beam (EB) lithography (only for S/D) and EB evaporation of Ti 20 nm/Au 60 nm and Cr 20 nm/Au 100 nm, respectively. Many reports discuss the difficulty and mechanism of ALD on 2D materials [20]–[22], and they suggest the solutions such as UV/O<sub>3</sub> functionalization [23] or introduction of buffer layers [17], [24], [25]. Third, the surfaces of the HfS<sub>2</sub> flakes were pretreated by UV/Ozone for 30 s, to clean up the resist residue from the surface with the partial oxidation of HfS<sub>2</sub>. The self-limiting layer-by-layer oxidation of TMD was reported for WSe<sub>2</sub> [26]. In the case of HfS<sub>2</sub>, there is a possibility of the formation of HfO<sub>x</sub> layer on HfS<sub>2</sub> with the sacrifice of few surface layers. If the assumption is correct, the ozone-treated HfS2 surface has the seed layer, which may be suitable for the ALD of HfO<sub>2</sub>. After a long exposure to ozone (e.g. 10 m), the conductivity of the few-layered HfS2 almost vanished owing to the full oxidation of the HfS2 layers. On the other hand, the effects of 30 s UV/O<sub>3</sub> treatment on  $I_D - V_{GS}$  characteristics were negligible or slight in the measurement of bare HfS<sub>2</sub> devices (not shown). The samples were then loaded into the ALD chamber and encapsulated by HfO2 at 150 °C using the precursors of Tetrakis(dimethylamino)Hafnium (TDMAH) and H<sub>2</sub>O for 200 cycles. The contact holes to S/D electrodes were formed by CF<sub>4</sub> reactive ion etching of HfO<sub>2</sub> with the etching mask of PMMA patterned by EB lithography. Finally, vacuum annealing was carried out at 250 °C for 10 min to improve the HfS<sub>2</sub>/HfO<sub>2</sub> interface and contact properties. The fabricated devices were measured in atmosphere using the semiconductor parameter analyzer.

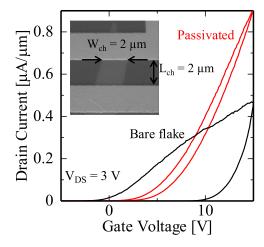

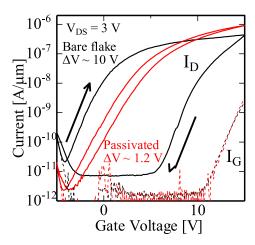

# III. REDUCTION OF HYSTERESIS

Fig. 3 indicates the transfer characteristics of the bare (black) and passivated (red) HfS $_2$  MOFETs with similar back gate structures (30-nm-thick Al $_2$ O $_3$ /Si) in (a) linear and (b) semi-log plots. The inset SEM image in (a) is the measured sample for the passivated device. The channel length  $L_{ch}$  and width  $W_{ch}$  were estimated to be 2  $\mu$ m. In the case of the bare device,  $L_{ch}$  was the same as that of the passivated device. Although  $W_{ch}$  was different for the two devices, all properties were normalized by  $W_{ch}$ .

Fig. 3. Comparison of the hysteresis of the transfer curves between bare and HfO<sub>2</sub> passivated HfS<sub>2</sub> MOSFETs. (a) Transfer characteristics in linear plot (b) Transfer characteristics in semi-log plot.

The maximum drain current at  $V_{DS}=3~{\rm V}$  and  $V_{GS}=15~{\rm V}$  was 0.9  $\mu{\rm A}/\mu{\rm m}$  for the passivated device. Although the drain current for many devices obtained by the passivation process showed a trend of being higher than the bare HfS<sub>2</sub>, the effect of passivation on the enhancement of the drain current is not yet clear owing to process fluctuation. The threshold voltage of the HfS<sub>2</sub> FET was over 0 V, and the enhancement mode n-type carrier transport was observed.

A typical bare  $HfS_2$  sample, which was exposed to air during the measurement, showed a significant voltage shift  $\Delta V$  of around 10 V between the forward and backward sweep in the hysteresis measurement. In contrast, the  $HfO_2$  passivated device fabricated in this study showed a suppressed  $\Delta V$  of less than 1.2 V. This significant reduction in hysteresis by surface passivation suggests that the greater part of the charge trapping occurred on the outermost surface of the  $HfS_2$  flake. The trap state densities simply estimated by the hysteresis  $\Delta V$  and oxide capacitance were over  $10^{13}$  cm $^{-2}$  for the bare sample and less than  $2 \times 10^{12}$  cm $^{-2}$  for the passivated sample. The remaining trap charges in the passivated device existed at the interface between  $HfS_2$  and  $Al_2O_3$  or in bulk  $Al_2O_3$ . For further reduction

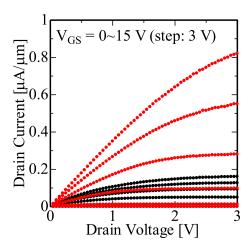

Fig. 4. Output characteristics of HfO<sub>2</sub> passivated MOSFET.

of trap charges, the development of the back-gate insulator and surface treatment before mechanical exfoliation, and the improvement of the interface after transfer should be investigated.

The gate leakage current of the fabricated devices is simultaneously plotted in Fig. 3(b). Under strong bias ( $V_{GS} < -3$  V or  $V_{GS} > 10$  V), the gate current increased exponentially. This gate leakage current and breakdown of the insulator could occur between the S/D pad and the n<sup>+</sup>-Si back gate, and it limits the maximum drain current through the allowable gate voltage. The increase in the drain current observed at the back bias region ( $V_{GS} < -3$  V) is almost similar to the gate leakage curve and it does not indicate hole conduction. Particularly in the passivated device, the gate leakage floor seems to limit the observable on/off ratio. The improvement in the quality of ALD Al<sub>2</sub>O<sub>3</sub> will be required for not only the reduction of charge traps but also superior insulating properties.

Fig. 4 shows the output characteristics of the HfO $_2$  passivated device. Robust current saturation behaviors were observed for both devices, with and without passivation. The drain current at  $V_{DS}=3$  V and  $V_{GS}=15$  V was around 0.82  $\mu$ A/ $\mu$ m for the passivated device and 0.16  $\mu$ A/ $\mu$ m for the bare device. The difference of drain current between the transfer and output characteristics with the same bias condition was around 10%. It was contrary to bare devices, which shows over a two times difference between the transfer and output measurement. This mismatch of the drain current, which depends on the bias history, also indicates high-density trap states.

Moreover, the time-dependent degradation of the drain current in the atmosphere was prevented by the  $HfO_2$  capping. One month after the exfoliation and  $HfO_2$  deposition, many devices indicated the drain current density of sub-microampere or a few microampere/ $\mu$ m without a severe decrease, in contrast to the bare devices [19]. Therefore, the ALD of  $HfO_2$  seems to provide good protection from the oxidation and absorption of several types of contaminants from the atmosphere.

# IV. VACUUM ANNEALING OF HFO2 PASSIVATED FET

Previously, we reported the current enhancement of HfS<sub>2</sub> FET using vacuum annealing to remove surface contaminants and

Fig. 5. Effects of vacuum annealing on  $I_D-V_{GS}$  characteristics of HfO2 passivated HfS2 MOSFET.

reduce contact resistance between Ti and HfS<sub>2</sub> [19]. In the case of the bare HfS<sub>2</sub>, the optimum annealing temperature was estimated to be 250 °C. At an annealing temperature of 350 °C, the device performance degraded severely. This degradation may be caused by the removal of S atoms from the surface and the formation of a disordered crystal structure. According to that result, the annealing temperatures of both the bare and passivated samples discussed in Section III were set at 250 °C. Capping layers could allow higher tolerance because the top insulator prevents the movement of atoms. Therefore, we reinvestigated the effect of vacuum annealing for the HfO<sub>2</sub> passivated devices.

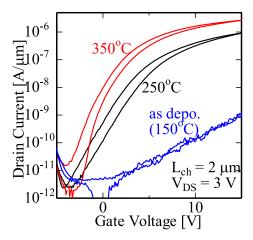

Fig. 5 shows the effects of vacuum annealing on the  $I_D - V_{GS}$ characteristics of the HfO2 covered HfS2 FET. Three curves were observed for the same device. The first I-V measurement was carried out after HfO2 deposition and the formation of contact holes. The "as deposited" device in this experiment was exposed to annealing at 150 °C for approximately 1 h in Ar ambient through the deposition process in the ALD chamber. The gate modulation of the drain current of the "as deposited" device was quite small with a maximum drain current of only 1 nA/ $\mu$ m and an on/off ratio of 100. Next, the sample was annealed at 250 °C for 10 m in a vacuum tube furnace. The drain current was significantly increased (0.9  $\mu$ A/ $\mu$ m) by the annealing as shown in the above section and mentioned in our previous report for bare HfS<sub>2</sub>. Then, the additional annealing was performed again at 350 °C. Further increase of the drain current to 2  $\mu$ A/ $\mu$ m and current slope in the subthreshold region were obtained compared to 250 °C. The hysteresis was also reduced slightly except for the very low current region, which was affected by the gate leakage properties. From these results, the effects of annealing are expected to decrease the contact resistance and achieve a better quality interface. Thus, HfO<sub>2</sub> capped HfS<sub>2</sub> indicated the improvement of current properties by higher temperature annealing at 350 °C.

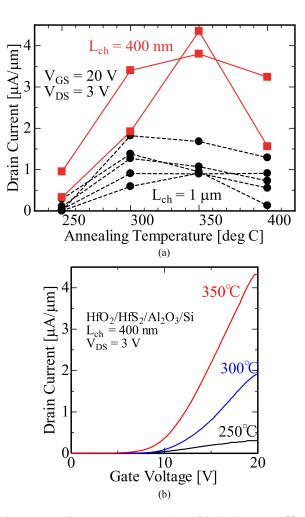

For a detailed investigation of the optimum annealing temperature, some devices fabricated on a 40-nm-thick  $Al_2O_3$  were measured with different annealing temperature of 250, 300, 350, and 400 °C. Fig. 6(a) plots the drain current at  $V_{\rm DS}=3~V$  and  $V_{\rm GS}=20~V$  for six devices. All devices showed a clear current

Fig. 6. (a) Annealing temperature dependence of the drain current at  $V_{GS}=20~\rm V$  and  $V_{DS}$  of 3 V for several devices with the two types of channel length  $\rm L_{ch}$ . (b)  $I_D-V_{GS}$  characteristics of the HfO<sub>2</sub> passivated HfS<sub>2</sub> transistor with different annealing temperature of 250, 300, and 350 °C for the same sample. (a) Comparison for several devices (b) Transfer characteristics.

increase with a increase in the annealing temperature from 250 to 300 °C. On the other hand, from 300 to 350 °C, half of the samples indicated enhancement and the others showed diminishment. At the annealing temperature of 400 °C, the drain current deteriorated for almost all devices. Therefore, the annealing temperature of HfO2 capped HfS2 should be set between 300 and 350 °C. This optimum range of annealing temperature might be caused by two different phenomena effects in HfS2 FET as mentioned below. The high temperature may improve the interface of Ti/HfS2 (S/D contact) and HfS2/Al2O3. However, it also has a possibility to harm HfS2 itself or cause the diffusion of metal atoms into HfS2.

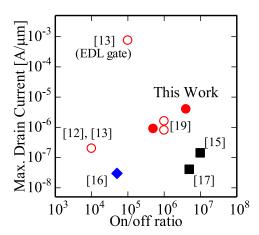

Fig. 6(b) describes the annealing temperature dependent transfer curves for one device, which shows the highest drain current in this experiment. The maximum drain current of 4.3  $\mu$ A/ $\mu$ m was accomplished with an annealing temperature of 350 °C. The drain current was higher than the values in previous reports about HfS<sub>2</sub> FET with a solid gate structure [12], [13], [16]–[19]. The extracted effective mobility was less than 1 cm²/Vs for this device. It was comparable to our previous works. All HfS<sub>2</sub> FETs have not resulted in expected

Fig. 7. Benchmarking of the device performance of HfS<sub>2</sub> FETs in previous reports. All dots plot the maximum drain current for each bias condition and on/off ratio between the maximum and minimum drain current.

high mobility yet as there are many factors that limit mobility; for example, impurity scattering, contact resistance, interface quality, and additional scattering processes [27].

Fig. 7 describes the benchmarking of  $HfS_2$  FET focused on the maximum drain current and on/off ratio. The  $HfO_2$  passivation and vacuum annealing discussed in this paper contributed in improving the drain current. However, its value was still  $\sim \! 100$  times smaller than the  $HfS_2$  FET with electric double layer gate structure [13] and other matured layered materials (e.g.,  $MoS_2$  [28], Phosphorene [29]). Further development of the fabrication process and the investigation of physical properties are required to achieve high performance with an  $HfS_2$  system.

# V. CONCLUSION

We investigated the effect of surface passivation for HfS<sub>2</sub> MOSFETs using ALD HfO<sub>2</sub>, to improve the stability of the I-V characteristics. The maximum drain current of 0.9  $\mu$ A/ $\mu$ m was observed at  $V_{DS}=3$  V and  $V_{GS}=15$  V. The hysteresis width  $\Delta$ V decreased apparently by the passivation from 10 V to 1.2 V. The protection of the surface by the high-k insulator is an efficient way to reduce the trap charges and improve stability. The vacuum annealing at 300-350 °C improved the drain current to 4.3  $\mu$ A/ $\mu$ m for HfO<sub>2</sub> capped HfS<sub>2</sub> FET.

# ACKNOWLEDGMENT

The author would like to thank Associate Prof. K. Nagashio for the helpful discussions and comments and Mr. S. Tamura for the technical support with the EB lithography.

### REFERENCES

- K. S. Novoselov et al., "Electric field effect in atomically thin carbon films," Science, vol. 306, no. 5696, pp. 666–669, Oct. 2004.

- [2] K. S. Novoselov et al., "Two-dimensional gas of massless Dirac fermions in graphene," Nature, vol. 438, no. 7065, pp. 197–200, Sep. 2005.

- [3] K. I. Bolotin et al., "Ultrahigh electron mobility in suspended graphene," Solid State Commun., vol. 146, no. 9–10, pp. 351–200, Mar. 2008.

- [4] F. Xia, D. B. Farmer, and P. Avouris, "Graphene field-effect transistors with high on/off current ratio and large transport band gap at room temperature," *Nano Lett.*, vol. 10, no. 2, pp. 715–718, Jan. 2010.

- [5] B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kiss, "Single-layer MoS<sub>2</sub> transistors," *Nature Nanotechnol.*, vol. 6, no. 3, pp. 217–218, Jan. 2011.

- [6] S. Kim et al., "High-mobility and low-power thin-film transistors based on multilayer MoS<sub>2</sub> crystals," Nature Commun., vol. 3, Aug. 2012, Art.ID. 1011

- [7] W. S. Hwang et al., "Transistors with chemically synthesized layered semiconductor WS<sub>2</sub> exhibiting 10<sup>5</sup> room temperature modulation and ambipolar behavior," Appl. Phys. Lett., vol. 101, no. 1, Jul. 2012, Art.ID. 013107.

- [8] W. Liu, J. Kang, D. Sarkar, Y. Khatami, D. Jena, and K. Banerjee, "Role of metal contacts in designing high-performance monolayer n-type WSe<sub>2</sub> field effect transistors," *Nano Lett.*, vol. 13, no. 5, pp. 1983–1990, Mar. 2013.

- [9] D. L. Greenaway and R. Nitsche, "Preparation and optical properties of group IV–VI<sub>2</sub> chalcogenides having the CdI<sub>2</sub> structure," *J. Phys. Chem. Solids*, vol. 26, no. 9, Sep. 1965, Art.ID. 213116.

- [10] W. Zhang, Z. Huang, W. Zhang, and Y. Li, "Two-dimensional semiconductors with possible high room temperature mobility," *Nano Res.*, vol. 7, no. 12, pp. 1731–1737, Dec. 2014.

- [11] C. Gong, H. Zhang, W. Wang, L. Colombo, R. M. Wallace, and K. Cho, "Band alignment of two-dimensional transition metal dichalcogenides: Application in tunnel field effect transistors," *Appl. Phys. Lett.*, vol. 103, no. 5, Aug. 2013, Art.ID. 053513.

- [12] T. Kanazawa, T. Amemiya, A. Ishikawa, K. Tsuruta, T. Tanaka, and Y. Miyamoto, "Fabrication of thin-film HfS<sub>2</sub> FET," in *Proc. 2015 73rd Device Res. Conf.*, 2015, pp. 217–218.

- [13] T. Kanazawa et al., "Few-layer HfS<sub>2</sub> transistors," Sci. Rep., vol. 6, Mar. 2016, Art.ID. 22277.

- [14] J. Chang, "Modeling of anisotropic two-dimensional materials monolayer HfS<sub>2</sub> and phosphorene metal-oxide semiconductor field effect transistors," *J. Appl. Phys.*, vol. 117, no. 21, Jun. 2015, Art.ID. 214502.

- [15] K. Xu et al., "Ultrasensitive phototransistors based on few-layered HfS<sub>2</sub>," Adv. Mater., vol. 27, no. 47, pp. 7781–7887, Oct. 2015.

- [16] S. H. Chae et al., "Oxidation effect in octahedral hafnium disulfide thin film," ACS Nano, vol. 10, no. 1, pp. 1309–1316, Jan. 2016.

- [17] K. Xu et al., "Toward high-performance top-gate ultrathin HfS<sub>2</sub> field-effect transistors by interface engineering," Small, vol. 12, no. 23, pp. 3106–3111, Apr. 2016.

- [18] B. Zheng et al., "Vertically oriented few-layered HfS<sub>2</sub> nanosheets: Growth mechanism and optical properties," 2D Mater., vol. 3, no. 3, Sep. 2016, Art ID, 035024

- [19] V. Upadhyaya, T. Kanazawa, and Y. Miyamoto, "Vacuum annealing and passivation of HfS<sub>2</sub> FET for mitigation of atmospheric degradation," in *Proc. 2016 Asia-Pac. Workshop Fundam. Appl. Adv. Semicond. Devices*, 2016, pp. 231–235.

- [20] X. Wang, S. M. Tabakman, and H. Dai, "Atomic layer deposition of metal oxides on pristine and functionalized graphene," *J. Amer. Chem. Soc.*, vol. 130, no. 26, pp. 8152–8153, May 2008.

- [21] H. Liu, K. Xu, X. Zhang, and P. D. Ye, "The integration of high-k dielectric on two-dimensional crystals by atomic layer deposition," *Appl. Phys. Lett.*, vol. 100, no. 15, Apr. 2012, Art.ID. 152115.

- [22] S. McDonnell et al., "HfO<sub>2</sub> on MoS<sub>2</sub> by atomic layer deposition: adsorption mechanisms and thickness scalability," ACS Nano, vol. 7, no. 11, pp. 10354–10361, Oct. 2013.

- [23] A. Azcatl et al., "MoS<sub>2</sub> functionalization for ultra-thin atomic layer deposited dielectrics," Appl. Phys. Lett., vol. 104, no. 11, Mar. 2014, Art.ID. 111601.

- [24] X. Zou et al., "Interface engineering for high-performance top-gated MoS<sub>2</sub> field-effect transistors," Adv. Mater., vol. 26, no. 36, pp. 6255–6261, Jul. 2014.

- [25] N. Takahashi, K. Watanabe, T. Taniguchi, and K. Nagashio, "Atomic layer deposition of Y<sub>2</sub>O<sub>3</sub> on h-NB for a gate stack in graphene FETs," *Nanotechnology*, vol. 26, no. 17, Apr. 2015, Art.ID. 175708.

- [26] M. Yamamoto et al., "Self-limiting layer-by-layer oxidation of atomically thin WSe<sub>2</sub>," Nano Lett., vol. 15, no. 3, pp. 2067–2073, Feb. 2015.

- [27] M. V. Fischetti and W. G. Vandenberghe, "Mermin-Wagner theorem, flexural modes, and degraded carrier mobility in two-dimensional crystals with broken horizontal mirror symmetry," *Phys. Rev. B*, vol. 93, no. 15, Apr. 2016, Art.ID. 155413.

- [28] L. Yang et al., "High-performance MoS<sub>2</sub> field-effect transistors enabled by chloride doping: Record low contact resistance (0.5 kΩ·μm) and record high drain current (460 μA/μm)," in Proc. 2014 Symp. VLSI Tech. Digest, 2014, pp. 192–193.

[29] L. Li, M. Engel, D. B. Farmer, S. Han, and H.-S. P. Wong, "High-performance p-type black phosphorous transistor with scandium contact," ACS Nano, vol. 10, no. 4, pp. 4672–4677, Mar. 2016.

**Toru Kanazawa** received the Ph.D. degrees in electronics and applied physics from the Tokyo Institute of Technology, Tokyo, Japan, in 2007.

He is an Assistant Professor in the Department of Electronics and Electrical Engineering, Tokyo Institute of Technology. His research interests include physics of transistors based on III–V compounds and two-dimensional layered semiconductors.

Kenji Tsuruta received the Ph.D. degree from the University of Tokyo, Tokyo, Japan, in 1994, and the D.Sci. degree. He became a Postdoctoral Fellow with the Louisiana State University (Department of Physics and Astronomy). In 1998, he was appointed a Lecturer at Okayama University, Okayama, Japan, where he is currently a Professor in the Graduate School of Natural Science and Technology. His research interests include theoretical and computational design of nanomaterials and nanodevices.

**Tomohiro Amemiya** (S'06–M'09) received the B.S., M.S., and Ph.D. degrees in electronic engineering from the University of Tokyo, Tokyo, Japan, in 2004, 2006, and 2009, respectively.

In 2009, he moved to the Quantum Electronics Research Center, Tokyo Institute of Technology, as an Assistant Professor. Since 2016, he has been an Assistant Professor with the Institute of Innovative Research, Tokyo Institute of Technology, Tokyo, Japan. His research interests include physics of photonic integrated circuits, metamaterials for optical frequen-

cies, semiconductor light-controlling devices, and the technologies for fabricating these devices.

Dr. Amemiya is a member of the Optical Society of America, the American Physical Society, and the Japan Society of Applied Physics. He received the 2007 IEEE Photonics Society Annual Student Paper Award, the 2008 IEEE Photonics Society Graduate Student Fellowships, the 2012 Konica Minolta Imaging Award, the 2015 Yazaki Memorial Foundation Award, and the 2016 Young Scientists' Prize, the Commendation for Science and Technology by the Minister of Education, Culture, Sports, Science and Technology.

Vikrant Upadhyaya received the B.S. degree from IIITDM Jabalpur, Jabalpur, India, in 2013. He is currently working toward the M.S. degree in physical electronics at the Tokyo Institute of Technology, Tokyo, Japan.

He is currently engaged in research on field effect transistors based on 2-D materials.

Takuo Tanaka received the B.Sc. degree in 1991 from the Department of Applied Physics, Faculty of Engineering, Osaka University, Suita, Japan, where he then received M.Sc. and Ph.D. degrees in applied physics, in 1993 and 1996, respectively. In 1996, he joined the Department of Electrical Engineering, Faculty of Engineering Science, Osaka University, as an Assistant Professor. In 2003, he moved to Nanophotonics Laboratory, RIKEN as a Research Scientist. He was promoted to Associate Chief Scientist in 2008 and working as the Head of Metamaterials Labora-

tory, RIKEN, and from 2014 he concurrently serves as a Team Leader of Innovative photon manipulation research team in RIKEN Center for Advanced Photonics. His research background is three-dimensional microscopy such as confocal microscope and two-photon microscope. He applied these three-dimensional microscope techniques not only observing 3-D microstructures of the samples but also fabricating 3-D micro/nanostructures or 3-D optical storage that records and reads digital data in the volume materials. He developed two-photon reduction technique that enables us to fabricate arbitrary 3-D metal nanostructures and this technique is known as ingenious technology of his group in this research community. Recently, he is also developing new nanofabrication techniques that incorporate self-organized formation of metal ring structures using hybridization of artificially designed DNA molecules or using magnetic interaction of magnetically functionalized metal nanoparticles. He has also experimental and theoretical experience in high precision optical measurements and spectroscopy, and numerical simulation of large-scale models of the interaction of light with structured materials.

He is a member of the Optical Society of America and the Japan Society of Applied Physics.

Atsushi Ishikawa received the Ph.D. degree in engineering from the Department of Applied Physics, Osaka University, Suita, Japan, in 2007. From 2007 to 2008, he was a Japan Society for the Promotion of Science Postdoctoral Fellow for Research Abroad, based in the University of California Berkeley, CA, USA, where he became a Postdoctoral Scholar in 2009. From 2010 to 2012, he was a Special Postdoctoral Researcher at RIKEN, Japan, where he became a Contract Researcher in 2013. Since 2014, he has been with Okayama University, Okayama, Japan as

an Assistant Professor. His research interests include metamaterials, plasmonics, and nanophotonics.

He is a member of the Optical Society of America and the Japan Society of Applied Physics.

Yasuyuki Miyamoto (M'88–SM'08) received the Ph.D. degree in physical electronics from the Tokyo Institute of Technology, Tokyo, Japan, in 1988.

He is a Professor in the Department of Electrical and Electronic Engineering, Tokyo Institute of Technology. He is currently engaged in research on semiconductor electronic devices and nanometer fabrication technology.