## Material Report —R&D—

# 二次元材料 HfS₂ を用いた MOS トランジスタ

金澤 徽\*1 雨宮 智宏\*2 宮本 恭幸\*3

単原子層までのチャネル薄層化が可能な二次元層状物質は将来の極短チャネル MOS トランジスタへの応用が期待されている。本稿では、新たな二次元材料である HfS<sub>2</sub> についてトランジスタへの応用を主眼に、半導体材料としての基本的な物性、試作したトランジスタの特性や今後の課題など、筆者らの取り組みを中心に紹介する。

## 1. はじめに

MOS トランジスタは LSI を構成する基幹部品 であり、現在の CPU ダイにおいてはチップ内に 十数億個のトランジスタが集積化されている。演 算能力の向上と消費電力の削減の観点からトラン ジスタに要求される性能は. 低い動作電圧で大き な駆動電流と小さな漏れ電流を実現することであ る。トランジスタの低電圧化と高電流化は、長年 にわたってスケーリング (比例縮小) 則に基づく 研究開発により達成されてきた。スケーリング則 は素子の厚さや長さ、幅といった設計サイズを同 じ比率で縮小化することで消費電力を保ちながら 集積度と動作速度が向上する、という原則による。 しかし、素子サイズの縮小化に伴う短チャネル効 果により漏れ電流が抑えられなくなると消費電力 が増加するため、同時にこれを抑制することが重 要である。近年の極微細化された素子サイズにお いては短チャネル効果の抑制はますます困難とな っている。その対策として開発世代ごとに、歪シ

リコン技術、High-k / メタルゲート技術、マルチゲート構造、といった新技術を逐次導入することで、集積密度と素子性能の向上が維持されている。今日の LSI 用 FET において電流を制御する領域であるチャネル長のスケーリングは 20 nm 前後まで到達しており、今後 10 nm 以下へとさらなる縮小化が進められると予想される 1)。現在、これを実現するための新たな集積化技術の開発が必要とされている。

短チャネル効果を抑制する有力な手法の一つとしてチャネルの薄層化がある。ここで 10 nm のチャネル長を考えるとチャネル厚さは数 nm 以下まで薄層化されることが望まれる。一方でシリコンを初めとする従来の半導体材料においてはチャネル厚を 3 nm 以下とした場合表面の平坦性に強い影響を受け、顕著な移動度の劣化が観測されるという問題がある 2)。層状物質は共有結合やイオン結合といった強固な原子間結合が二次元面内で完結しており、原子層間は弱いファンデルワールス力によって結び付けられている。このため膜厚の

機 能 材 料 2016年9月号 Vol.36 No.9

お名前・ご所属ご確認下さい

初校

<sup>\*1</sup> Toru Kanazawa 東京工業大学 工学院 電気電子系 助教

<sup>\*2</sup> Tomohiro Amemiya 東京工業大学 科学技術創成研究院 未来産業技術研究所 助教

<sup>\*3</sup> Yasuyuki Miyamoto 東京工業大学 工学院 電気電子系 教授

揺らぎがない単原子層の剥離や成膜を実現することが可能な材料として注目されている。最も有名な層状物質であるグラフェンは単原子層構造において200,000 cm²/Vs以上の室温移動度が予測されており³)、これらはバルク状態でのシリコンを大きく上回る値である。この優れた伝導特性と、二次元構造に由来する種々の特異な物性により、トランジスタを初めとする電子デバイスや各種センサ類といった様々な応用が検討され、一つの技術分野を築いている。一方で完全な状態の単原子層グラフェンはバンドギャップを持たないことから、論理回路用トランジスタにおいてはオフ電流を抑えることが困難である。

オフ電流を削減する観点からバンドギャップを有する層状物質として二硫化モリブデン( $MoS_2$ )が研究されている  $^4$ 。 $MoS_2$  は遷移金属ダイカルコゲナイドと呼ばれる物質群に属しており、 $\sim 1.8$  eV と比較的大きなバンドギャップを持つため高いオン/オフ比でのデバイス動作が可能である。一方で、単原子層の  $MoS_2$  は電子移動度が数百  $cm^2$ / Vs 程度に制限されるという理論計算が報告されており、トランジスタの低電圧化・高速化のためにはより高いことが望ましい。

理論計算において一部の遷移金属ダイカルコゲ ナイド材料は1,000 cm<sup>2</sup>/Vs を上回る電子移動度 を有する可能性が報告され、この値を原子層厚に おいて実現することができれば極短チャネルデバ イスの材料として大きな優位性が得られる。筆者 らはこの観点から将来のチャネル材料候補として 二硫化ハフニウム(HfS<sub>2</sub>)の持つ可能性に着目し た。単原子層 HfS2 は上記計算において1,800 cm<sup>2</sup>/Vs<sup>5)</sup>の移動度が期待されているとともに、バ ンドギャップにおいても 1.2 eV<sup>6)</sup> が見込まれてお り、これらの値はいずれもバルクのシリコンを上 回ることから, チャネル材料として優れた性質が 期待されている。一方で、バルクの HfS2 は高い抵 抗率を示すことが知られ、従来は半絶縁性の材料 と考えられていたため、これまで半導体デバイス への応用は試みられてこなかった。本稿では、こ の HfS。の半導体デバイス応用へ向けた、極薄膜薄

片の抽出や基礎物性評価、試作した電界効果トランジスタの特性について報告する。

## 2. 二硫化ハフニウムの基本的性質

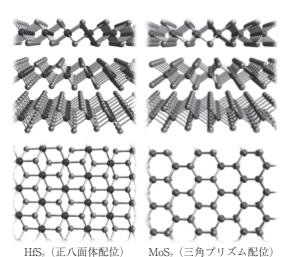

HfS<sub>2</sub> は他の二次元層状物質と同様に原子層間は弱いファンデルワールス結合によって結びついており、容易に劈開分離することが可能である。一原子層内においては遷移金属原子である Hf の周囲にカルコゲン原子 S が正八面体配位で並んだ  $CdI_2$ 型の二次元結晶構造を有しており  $^7$ ,  $MoS_2$  や  $WS_2$  がイオン結合性の強さから三角プリズム型配位の結晶構造を取りやすいという傾向とは異なる。図 1 は  $HfS_2$  および  $MoS_2$  の二次元結晶構造の模式図である。 $HfS_2$  単原子層の厚さは 0.59 nm であり  $^8$  , 各層の Hf 原子が平面内の同じ位置に積層される構造が安定となる。

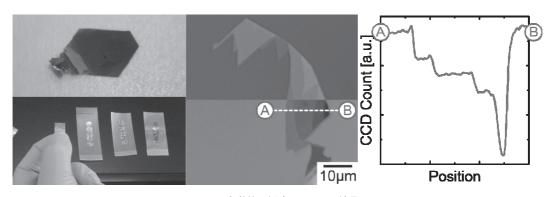

図2は厚さの異なる様態におけるHfS<sub>2</sub>結晶の光学撮影像を表している。HfS<sub>2</sub>のバルク結晶は光沢を有する赤褐色ないし紫褐色の固体であり、一般に化学合成によって生成される。この状態でHfS<sub>2</sub>結晶表面に対して水滴を利用した接触角測定を行った結果、接触角は約90°を示し、表面の疎水性が確認された。本稿においてはこのバルク結晶から原子層厚さのHfS<sub>2</sub>小片を得るために、粘着テープ上での薄層化後に粘着テープを転写基板に貼り

図1 遷移金属ダイカルコゲナイドの二次元結晶

図2 光学的に観察した HfS<sub>2</sub> 結晶

付けて引き剥がすことで転写を行う機械的剥離法 を用いている。転写先の基板としては絶縁膜 (Al<sub>2</sub>O<sub>3</sub> またはSiO<sub>2</sub>)を堆積したシリコンを用いて いる。転写に際しては紫外線オゾン洗浄によって 表面の有機汚染物を除去した後に、絶縁膜表面に ヘキサメチルジシラザン (HMDS) の滴下により 自己組織化単分子膜を形成し疎水性化処理を行う ことで、HfS₂結晶との親和性が向上し転写薄片の サイズおよび密度が増加することが確認された。 SiO<sub>2</sub>上の HfS<sub>2</sub>薄片を光学顕微鏡により観察したと ころ、白色光源下においても下地シリコン基板を 含む層構造からの反射光干渉により生じた. 層数 に依存した階段状のコントラスト変化が明瞭に観 察された。原子間力顕微鏡を用いた段差測定にお いてもコントラストの変化と対応する位置で1nm ~の段差が確認され、最も小さい段差は原子層ス テップに対応すると考えられる。これら表面観察 の結果より、従来の二次元系材料と同様に HfS。に おいても「スコッチ」テープを用いた機械的剥離 により、数 μm 以上の範囲で均一な原子層数を有 する二次元結晶が得られることが確認できた。

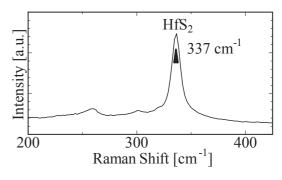

6原子層と推定される膜厚を有する  $HfS_2$  薄片の ラマン分光測定においては  $337 \, \mathrm{cm}^{-1}$  付近において ピークが観測された( $\mathbf{Z}$  3)。このラマンピークは バルク結晶における  $A_{1g}$  モード  $^{9)}$  とよく一致して おり, $260 \, \mathrm{cm}^{-1}$  に存在する微弱な  $E_{g}$  ピークについ ても同様に一致が見られた。この結果は,今回用 いた数原子層程度の厚さの超薄膜結晶においても バルクと同等の結晶構造が保たれていることを示

図3 HfS<sub>2</sub>極薄膜結晶からのラマンスペクトル

している。

## 3. HfS。を用いたトランジスタ

#### 3.1 バックゲートを用いたトランジスタ動作

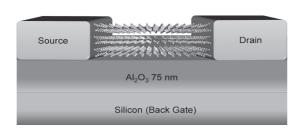

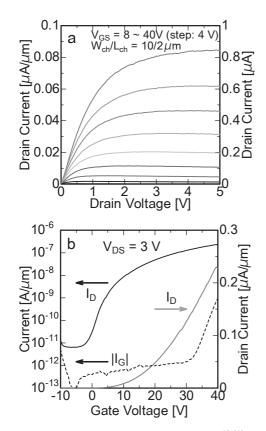

機械的剥離法によって得られた数原子層厚の  $HfS_2$  薄片を用いて図 4 に示すトランジスタ構造を 作製した。作製プロセスは以下のとおりである。  $Al_2O_3$  75 nm を原子層堆積法により成膜したシリコン基板上に転写した 3.8 nm の厚さ(6 原子層)を持つ  $HfS_2$  薄片上に,電子ビーム蒸着を用いて Ti 20 nm と Au 100 nm からなる電極を形成した。完成したデバイスに熱処理を行うことでコンタクトが改善し電流特性が向上する。図 5 は基板をゲート電極としたトランジスタの室温における電流特性である。ゲート電圧による依存するドレイン電流の変調を出力特性における明瞭な電流飽和特性が観測された。伝達特性は  $0.2\,\mu\text{A}/\mu\text{m}$  の最大ドレイン電流を示し,オン/オフ比として  $10^4\,\text{以上}$

図4 HfS。をチャネルとした電界効果トランジスタ

図 5 HfS<sub>2</sub>トランジスタ構造と電流特性 <sup>10,11)</sup>

の値が得られた。これらの結果は  $HfSe_2$ や  $ZrS_2$ を はじめとした新規二次元材料としては良好なトランジスタ特性を示しており、従来半絶縁性の物質 として考えられていた  $HfS_2$  が極薄膜において半導体チャネルとして機能することを初めて明らかとした  $^{10,11)}$ 。一方で、実効電子移動度の抽出を行ったところその値は  $0.1\,\mathrm{cm}^2/\mathrm{Vs}$  程度にとどまっており、期待した高移動度を得るには至っていない。また、電流値についても  $MoS_2$ や Phosphorene と

いった技術的に成熟した材料系と比較すると低い 値となっており、改善の必要がある。

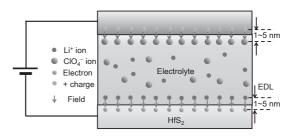

#### 3.2 電気二重層を用いたトランジスタ制御

機械剥離法により作製したバックゲートトラン ジスタの特性を制限する要因として、絶縁膜と層 状物質の界面品質の問題がある。絶縁膜表面のラ フネスに起因するキャリア散乱や制御性の低下. 基板表面に残った炭化水素をはじめとする各種汚 染物質の影響、絶縁膜中への電荷トラップといっ た影響により、測定されるデバイス性能は劣化し ている可能性がある。これら下部界面に起因する 劣化要因を回避する構造として LiClO4: PEO から なる電解質ゲルを用いた電気二重層(EDL)トラ ンジスタ構造 <sup>12)</sup> を採用した (**図 6**)。電解質を介 して正のゲート電圧を印加するとゲル内の遊離し たイオンが移動し、ゲートコンタクト近傍には陰 イオン(ClO<sub>4</sub>)が、チャネル表面付近には陽イオ ン (Li<sup>+</sup>) が配列し, 固体内の電荷と極薄い (1~ 5 nm) 間隔で対向する電気二重層を形成する。こ の電気二重層はその薄さから大きな静電容量を持 つとともに、原子層レベルで平坦かつ未結合手の ない層状物質表面と良好な界面を形成するため, 優れたゲート制御性を実現することができる。こ れを用いて作製したデバイスの特性を以下の図7 に示す 11,13)。容量の増加に伴って駆動電圧が削減 されているとともに、最大ドレイン電流は0.75 mA/μm が得られており、バックゲートでの動作 時と比較して1000倍程度まで向上し、バンドギャ ップを有する層状物質としては高い電流が得られ ている。この電流増加はゲート特性の改善により

図6 電気二重層トランジスタの動作原理

図7 電気二重層トランジスタの電流特性 11,13)

$HfS_2$ 内のキャリア濃度が大幅に向上したことが主要因と考えられる。低ドレイン電圧時の電流特性から抽出された電子移動度は電気二重層の厚さを $1\sim 5$  nm と仮定した場合  $16\sim 80$  cm²/Vs 程度と見積もられた。電流値同様にバックゲート動作と比較して高い値を示しているが,目標とする高移動度には到達していない。コンタクト部分の抵抗削減や,電解質ゲルの応答速度に対して十分に遅い速度での測定,ゲートコンタクト近傍における電圧降下といった要素を取り除くデバイス構造,測定シーケンスの導入により向上が期待される。電気二重層を用いたデバイスの動作については,前述した電流増加のメカニズムを含めて,より詳細な評価・検討を必要とする段階である。

## 4. 現在の課題と特性改善への取り組み

#### 4.1 現在の課題

HfS<sub>2</sub>のデバイス応用における問題は予想されている高移動度に比して作製したデバイスから抽出される電子移動度が低いという点である。これはデバイスの伝達コンダクタンスが低いという点から生じており、作製プロセスに由来の複数の要因により駆動能力が制限されていることに起因する。より具体的には、金属と半導体表面の間に生じるコンタクト抵抗が大きいこと、半導体表面への原子吸着や欠陥への電子トラップにより走行キャリ

アの散乱や可動キャリア濃度の低下が生じていること、HfS<sub>2</sub>層の結晶性に起因する移動度の劣化が代表的な劣化要因として考えられる。これらデバイス特性に影響する効果について、原因を特定し解消していくことが今後の特性向上へ向けた最大の課題である。

また、理論的な移動度の予測についても文献 5) において見積もられた散乱機構以外にも影響を及ぼす散乱の存在について別途提起する報告がなされており <sup>14)</sup>、ホール測定などを用いた実験的な評価を含めてさらなる検討を行うことが必要とされる。

#### 4.2 表面保護による特性の向上

本項では特性改善へ向けた現在の取り組みに関する一例について述べる。二次元材料のデバイス応用において留意すべき点として表面の不安定性が挙げられる。 $HfS_2$  についても筆者らを含むいくつかの報告  $^{15,16)}$  において大気中における特性の劣化が観測される場合が有る。その主な原因としては大気中の酸素や水分との反応による  $HfS_2$  原子層の酸化,表面への気体原子吸着によるキャリアの散乱が考えられる。この現象を抑制することを目的として原子層堆積法を用いて高誘電率絶縁膜である  $HfO_2$  を用いて, $HfS_2$  トランジスタの表面を保護・不活性化したデバイスの作製を行った。

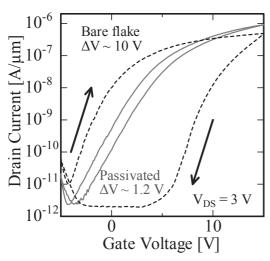

図8は作製したデバイスの伝達特性を示しているが、保護を行わない  $HfS_2$  が幅 10 V 以上という大きなヒステリシスを描いているのに対して、 $HfO_2$  キャップ層を用いた素子についてはヒステリシス幅が 1.2 V 以下まで明確に減少していることが確認できる 170。これは、デバイス動作時における $HfS_2$  表面への電子トラップが抑制された結果であると考えられ、同時に観測された事件経過による特性劣化の抑制効果や、ドレイン電流の増加とともに、 $HfO_2$  保護がデバイス特性の向上・安定化に対して有効であることを示す結果である。

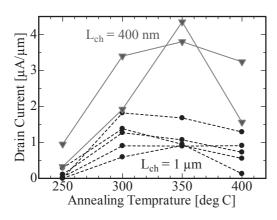

$HfO_2$ 保護をしたサンプルについて真空雰囲気中でのアニールを行ったところ  $300 \sim 350^{\circ}$  の温度範囲で電流密度の向上が確認された(**図 9**)。保護

図8 HfO。保護による特性の変化 17)

図9 HfS。トランジスタ電流のアニール温度依存性

を行わないサンプルについては 250 を超えた温度では電流密度が大きく低下し、トランジスタ動作が困難になる  $^{16)}$  という傾向とは異なっており、加熱による  $HfS_2$  結晶の劣化が  $HfO_2$  キャップにより抑制されたと考えることができる。このアニールにより最大の電流密度は  $4\,\mu\text{A}/\mu\text{m}$  にまで向上している。現在、さらなる高性能化のため、デバイス構造やプロセスを改善するための取り組みを行っている。

#### 4.3 今後の展望

以上述べてきたように HfS2 のデバイス応用に向

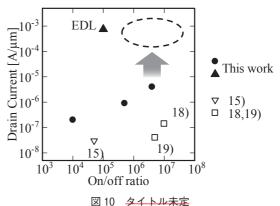

$HfS_2$ トランジスタの性能比較

けた取り組みは、その材料としての可能性を示唆する結果が得られつつある。一方で、従来の層状物質に対する利点を明らかとするためには、基礎物性の調査や、デバイス作製技術の進歩、より詳細な理論的検討など様々な取り組みが必要である。図10はこれまでに報告されている HfS2 トランジスタのオン/オフ比と最大ドレイン電流をプロットしたグラフである。前述した取り組みによりデバイス性能は向上しつつあるが、今後さらなる研究開発により電気二重層トランジスタで観測された特性を固体ゲート絶縁膜で実現することができれば、将来の超低消費電力トランジスタにおけるチャネル材料候補としての潜在能力の提示につながると考えている。

加えて  $HfS_2$  の有する特徴の一つとして  $MoS_2$  をはじめとする他の材料系と比較して大きな電子親和力を有するという点が挙げられる。この性質を利用することで二次元層状物質同士を用いたタイプ  $\mathbb{I}$  型のヘテロ接合への利用が期待されている。ヘテロ界面における顕著なバンド構造の変化は、量子効果を利用した各種デバイス構造において利点を有している。一例としてタイプ  $\mathbb{I}$  型のヘテロ接合はトンネルトランジスタ応用における高電流動作化  $\mathcal{O}$  応用が見込まれる。こういった観点からも  $HfS_2$  を用いたデバイス応用の展開が期待される。その他、 $HfS_2$  を用いた高感度なフォトトランジスタも動作が報告されており  $\mathbb{I}^{8,19}$ , フォトニクスデバイスとしても検討が行われている。

## 5. おわりに

本稿では、原子層エレクトロニクスにおける新 たな二次元半導体材料である HfS2 の基本的な性質 と試作したトランジスタの動作、将来の展望につ いて筆者らの研究に基づいて紹介させていただい た。単層グラフェンの抽出とその特異な電子物性 の報告以降、急速な発展を遂げた原子層物質に関 わる研究領域は、今なお発展途上の段階の研究領 域である。実用化に向けては基礎物性の解明、種々 のデバイス応用と用途に応じた材料選択、作製プ ロセス・大量合成の技術開発といった課題に対し て, 理論計算, 物性評価といった物性物理学に属 する範囲からナノ構造形成プロセス技術. デバイ スシミュレーションのような電子工学まで様々な 分野からのアプローチが必要となっている。今後 も電子工学の視点・技術基盤に基づいた研究開発 により, 極限的な性能を有するデバイス実現を目 指した取り組みを行う所存である。

謝辞:本稿で紹介した研究成果は、理化学研究所田中拓 男准主任研究員、岡山大学自然科学研究科鶴田健二教 授、同、石川篤助教、東京大学工学部長汐晃輔准教授 の協力・助言を受けながら行ったものである。また、一 部は総務省戦略的情報通信研究開発事業(SCOPE)お よび日本学術振興会科学研究費補助金・新学術領域 「原子層科学」公募研究による支援を受けて実施された。

#### 文 献

- International Technology Roadmap for Semiconductors

- K. Uchida, S. Takagi, Appl. Phys. Lett., 82, 2916

-2918 (2003)

- E. H. Hwang, S/ Adam, S. D. Sarma, *Phys. Rev. Lett.*, 98 186806 (2007)

- 4) B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, A. Kis, *Nat. Nanotech.*, **6**, 147–150

(2011)

- W. Zhang, Z. Huang, W. Zhang, Y. Li, *Nano Research*, 7, 1731–1737 (2014)

- C. Gong, H. Zhang, W. Wang, L. Colombo, R. M. Wallace, K. Cho, *Appl. Phys. Lett.*, **107**, 139904 (2015)

- M. Chhowalla, H. S. Shin, G. Eda, L.-J. Li., K. P. Loh, H. Zhang, *Nat. Chem.*, 5, 263–275 (2013)

- D. L. Greenaway, R. Nitsche, J. Phys. Chem. Solids, 26, 1445–1458 (1965)

- A. Cingolani, M. Lugarà, *Physica Scripta.*, **37**, 389

-391 (1988)

- 10) T. Kanazawa, T. Amemiya, A. Ishikawa, V. Upadhyaya, T. Tanaka, K. Tsuruta, Y. Miyamoto, 73 rd Device Research Conf., pp.217–218 (2015)

- T. Kanazawa, T. Amemiya, A. Ishikawa, V. Upadhyaya, T. Tanaka, K. Tsuruta, Y. Miyamoto, Sci. Rep., 6, 22277 (2016)

- 12) T. Fujimoto, K. Awaga, *Phys. Chem. Chem. Phys.*15, 8983 (2013)

- 13) T. Kanazawa, T. Amemiya, A. Ishikawa, V. Upadhyaya, T. Tanaka, K. Tsuruta, Y. Miyamoto, 2015 Int. Conf. Solid State Devices and Materials, pp.714-715 (2015)

- M. V. Fischetti, W. G. Vandenberghe, *Phys. Rev. B*,

155413 (2016)

- 15) S. H. Chae, Y. Jin, T. S. Kim, D. S. Chung, H. Na, H. Nam, H. Kim, D. J. Perello, H. Y. Jeong, T. H. Ly, Y. H. Lee, ACS Nano, 10, 1309–1316 (2016)

- 16) V. Upadhya, T. Kanazawa, Y. Miyamoto, 2016 Asia -Pacific Workshop on Fundamentals and Applications of Advanced Semiconductor Devices, A5-7 (2016)

- 17) T. Kanazawa, T. Amemiya, V. Upadhyaya, A. Ishikawa, T. Tanaka, K. Tsuruta, Y. Miyamoto, 16 th Int. Conf. Nanotechnology, to be presented (2016) ThAM11.3

- 18) K. Xu, Z. Wang, F. Wang, Y. Huang, F. Wang, L. Yin, C. Jiang, J. He, Adv. Mat., 27, 7881–7887 (2015)

- 19) K. Xu, Y. Huang, B. Chen, Y. Xia, W. Lei, Z. Wang, Q. Wang, F. Wang, L. Yin, J. He, Small, 12, 3106 -3111 (2016)